Декодерът е комбинационна верига изградени с логически порти. Това е обратната страна на енкодера. Декодерна схема се използва за трансформиране на набор от цифрови входни сигнали в еквивалентен десетичен код на изхода му. За „n“ входове декодерът дава 2 ^ n изхода. В тази статия ще обсъдим дизайна на схемата от 4 до 16 декодера, използвайки 3 до 8 декодера.

Енкодерът е комбинационна схема, която променя набор от сигнали в код. За „2 ^ n“ входове енкодерна схема дава „n“ изходи.

Следващата фигура показва блок-схемата на декодер.

Блок-схема на декодера

3 до 8 декодер

Тази схема на декодера дава 8 логически изхода за 3 входа. Веригата е проектирана с AND и NAND комбинации . Отнема 3 двоични входа и активира един от осемте изхода.

3 до 8 Блок-схема на декодера

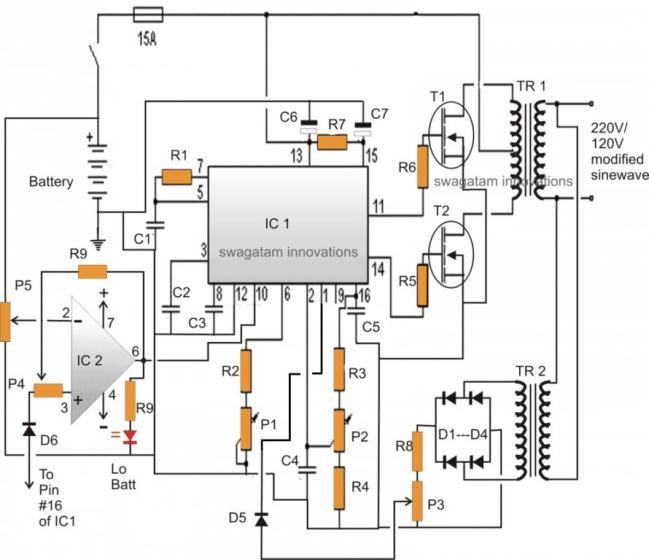

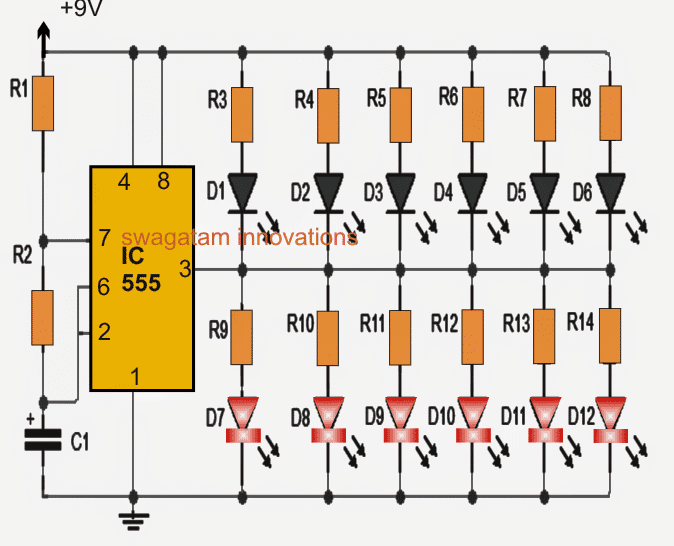

Електрическа схема

Схемата на декодера работи само когато щифтът Enable е висок.

3 до 8 Декодерна верига

Таблица на истината

Когато щифтът Enable (E) е нисък, всички изходни щифтове са ниски.

| S0 | S1 | S2 | Е | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

| х | х | х | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Дизайн на веригата от 4 до 16 декодера Използвайки 3 до 8 декодера

ДА СЕ декодер верига от по-високата комбинация се получава чрез добавяне на две или повече по-ниски комбинационни вериги. 4 до 16 декодерни вериги се получават от две 3 до 8 декодерни вериги или три 2 до 4 декодерни вериги.

Когато се комбинират две 3 до 8 декодерни вериги, разрешаващият щифт действа като вход за двата декодера. Когато щифтът за разрешаване е висок при една 3 до 8 декодерни вериги, тогава той е нисък при друга 3 до 8 декодерна верига.

Таблица на истината

ПИНът Enable (E) действа като един от входните щифтове и за двата 3 до 8 схеми на декодера.

| Е | ДА СЕ | Б. | ° С | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | Y8 | Y9 | Y10 | Y11 | Y12 | Y13 | Y14 | Y15 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Електрическа схема от 4 до 16 декодера

4 до 16 декодерна верига

Приложения на декодери

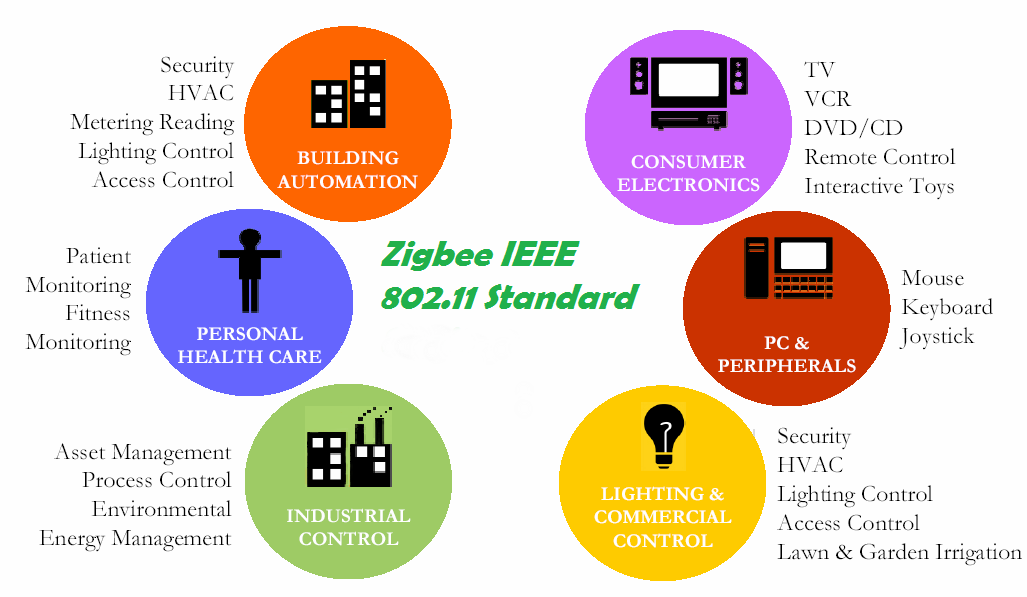

- Във всеки безжична комуникация , сигурността на данните е основната грижа. Декодерите са предназначени главно да осигурят сигурност за комуникация на данни чрез проектиране на стандартни алгоритми за криптиране и дешифриране.

- Декодерите се използват в аудио системи за конвертирате аналогов звук в цифрови данни.

- Използва се като декомпресор за преобразуване на компресирани данни като изображения и видеоклипове в декомпресирана форма.

- Декодерите използват електронни схеми, които преобразуват компютърните инструкции в контролни сигнали на процесора.

Следователно това е всичко за дизайна на схемата на декодера от 4 до 16, използвайки схема на декодера от 3 до 8. Освен това, всички въпроси относно тази статия или проекти за електроника можете да ни коментирате в раздела за коментари по-долу. тук е въпрос към вас, каква е ползата от Enable pin encoder / decoder?