JTAG (Joint Test Action Group) е утвърден стандарт IEEE 1149.1, който е разработен през 1980 г. за решаване на производствени проблеми, възникнали в електронни платки или печатни платки . Тази технология се използва за осигуряване на достатъчно тестов достъп за всяка сложна платка, когато тестовият достъп намалява. Така беше пусната технологията за гранично сканиране и стандартът JTAG или JTAG спецификация се установява. Сложността на електрониката се увеличава с всеки изминал ден, така че JTAG спецификацията се превърна в приет тестов формат за тестване на сложни и компактни електронни устройства. Тази статия обсъжда общ преглед на a JTAG протокол – работа с приложения.

Какво е JTAG?

Името, дадено на IEEE 1149.1 Standard Test Access Port, както и на архитектурата за гранично сканиране, е известно като JTAG (Joint Test Action Group). Тази архитектура за гранично сканиране се използва най-вече в компютъра процесори тъй като първият процесор с JTAG беше пуснат от Intel. Този стандарт IEEE просто определя как се тества веригата на компютъра, за да се потвърди дали работи правилно след процедурата на производство. На платките се извършват тестове за проверка на спойките.

Joint Test Action Group предоставя изглед на изводите за тестери с всяка IC подложка, което помага при идентифицирането на всякакви грешки в платката. След като този протокол е свързан с чип, това може да прикачи сонда към чипа, като позволи на разработчика да контролира чипа, както и връзките му с други чипове. Интерфейсът с групата Joint Test Action може също да се използва от разработчиците за копиране на фърмуера в енергонезависима памет на електронно устройство.

Конфигурация/извеждане

Групата за съвместно изпитване включва 20 щифта, като всеки щифт и неговата функция са обсъдени по-долу.

Pin1 (VTref): Това е щифтът за целево референтно напрежение, който се използва за свързване към основното захранване на целта, което варира от 1,5 до 5,0 VDC.

Pin2 (Vзахранване): Това е целевото захранващо напрежение, което се използва за свързване на основното захранващо напрежение от целеви 1,5 VDC – 5,0 VDC.

Pin3 (nTRST): Това е тестов щифт за нулиране, който се използва за нулиране на крайната машина на TAP контролера.

Щифтове (4, 6, 8, 10, 12, 14, 16, 18 и 20): Това са обикновени GND щифтове.

Pin5 (TDI): Това са тестови данни в щифта. Тези данни се прехвърлят в целевото устройство. Този щифт трябва да бъде изтеглен нагоре при определено състояние на целевата дъска.

Pin7 (TMS): Това е щифтът за състояние на тестовия режим, който се изтегля, за да се определи следващото състояние на крайната машина на TAP контролера.

Pin9 (TCK): Това е щифт за тестов часовник, който синхронизира операциите на вътрешната машина на състоянието в TAP контролера.

Pin11 (RTCK): Това е щифтът Input Return TCK, който се използва в устройства, които поддържат адаптивен такт.

Pin13 (TDO): Това е щифтът Test Data Out, така че данните се преместват от целевото устройство в Flyswatter.

Pin15 (nSRST): Това е щифтът за нулиране на целевата система, който е свързан към главния сигнал за нулиране на целта.

Щифтове 17 и 19 (NC): Това не са свързани щифтове.

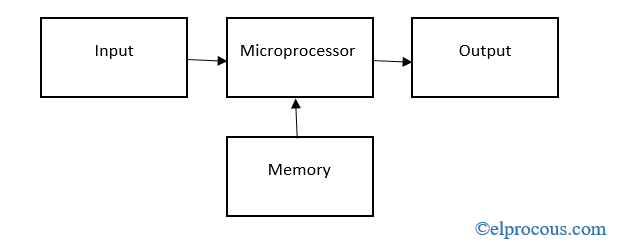

JTAG работи

Оригиналната употреба на JTAG е за гранично тестване. Ето една проста печатна платка, включваща две интегрални схеми като CPU и FPGA . Една типична платка може да включва много интегрални схеми. Като цяло интегралните схеми включват много изводи, които са свързани заедно с много връзки. Тук, в следващата диаграма, са показани само четири връзки.

Така че, ако проектирате много платки, където всяка платка има хиляди връзки. В това има някои лоши дъски. Така че трябва да проверим коя платка работи и коя не работи. За тази цел беше създадена групата за съвместни тестове.

Този протокол може да използва контролните щифтове на всички чипове, но в следващата диаграма Joint Test Action Group ще направи всички изходни щифтове на процесора и всички входни щифтове на FPGA. След това, чрез предаване на известно количество данни от щифтовете на процесора и четене на стойностите на щифтовете от FPGA, JTAG заявява, че връзките на печатната платка са наред.

Всъщност групата за съвместно тестване включва четири логически сигнала TDI, TDO, TMS и TCK. И тези сигнали трябва да бъдат свързани по определен начин. Първо, TMS & TCK са свързани паралелно към всички IC на JTAG.

След това TDI и TDO се свързват за образуване на верига. Както можете да видите, всяка съвместима с JTAG IC включва 4 пина, които се използват за JTAG, където 3 пина са входове, а 4-ти щифт е изход. Петият щифт като TRST не е задължителен. Обикновено JTAG щифтовете не се споделят за други цели.

Чрез използването на Joint Test Action Group, всички IC използват гранично тестване, чиято първоначална причина е създадена от JTAG. Понастоящем използването на този протокол е разширено, за да позволи различни неща като конфигуриране на FPGA и след това JTAG се използва в ядрото на FPGA за целите на отстраняване на грешки.

JTAG архитектура

Архитектурата JTAG е показана по-долу. В тази архитектура всички сигнали между основната логика на устройството и щифтовете се прекъсват чрез сериен път за сканиране, наречен BSR или регистър на гранично сканиране. Този BSR включва различни „клетки“ за гранично сканиране. Обикновено тези клетки за гранично сканиране не се виждат, но могат да се използват за задаване или четене на стойности в тестов режим от щифтовете на устройството.

Интерфейсът JTAG, наречен TAP или Test Access Port, използва различни сигнали за поддържане на операцията за гранично сканиране като TCK, TMS, TDI, TDO и TRST.

- Сигналът TCK или Test Clock просто синхронизира вътрешните операции на крайната машина.

- TMS или сигналът за избор на режим на тестване се взема при нарастващия фронт на тестовия тактов сигнал за вземане на решение за следващото състояние.

- Сигналът TDI или Test Data In означава преместените данни в логиката на друго програмиране на тестовото устройство. След като вътрешната държавна машина е в правилното състояние, тогава се взема проба при нарастващия ръб на TCK.

- Сигналът TDO или Test Data Out означава изместените данни на тестовото устройство в противен случай програмираща логика. След като вътрешната държавна машина е в правилното състояние, тогава тя е валидна на намаляващия ръб на TCK

- TRST или Test Reset е допълнителен щифт, който се използва за нулиране на крайната машина на TAP контролера.

TAP контролер

Тестовата точка за достъп в архитектурата на JTAG се състои от TAP контролер, регистър на инструкции и регистри на тестови данни. Този контролер включва тестовата държавна машина, която е отговорна за четенето на TMS и TCK сигналите. Тук i/p щифтът за данни се използва просто за зареждане на данни в граничните клетки между ядрото на IC и физическите щифтове, както и за зареждане на данни в един от регистрите за данни или в регистъра на инструкциите. Изводът за данни o/p се използва за четене на данни или от регистрите, или от граничните клетки.

Машината на състоянието на TAP контролера се управлява от TMS и се тактова от TCK. State machine използва два пътя за обозначаване на два различни режима като режим на инструкции и режим на данни.

Регистри

Има два вида регистри, налични в рамките на граничното сканиране. Всяко съвместимо устройство включва минимум два или повече регистъра за данни и един регистър за инструкции.

Регистър на инструкциите

Регистърът на инструкциите се използва за съхраняване на текущата инструкция. Така неговите данни се използват от TAP контролера, за да реши какво да изпълни с получените сигнали. Най-често данните в регистъра на инструкциите ще описват към кой от регистрите на данни трябва да бъдат предадени сигналите.

Регистри на данни

Регистрите на данни са налични в три вида BSR (регистър за гранично сканиране), регистър BYPASS & ID CODES. И също така може да има други регистри за данни, но те не са необходими като елемент от стандарта JTAG.

Регистър на гранично сканиране (BSR)

BSR е основният регистър на данните за тестване, който се използва за прехвърляне на данни от и към I/O щифтовете на устройството.

ОКОЛОВРЪСТЕН ПЪТ

Байпасът е еднобитов регистър, използван за предаване на данни от TDI – TDO. Така че позволява допълнителни устройства в рамките на верига да бъдат тествани с минимални разходи.

ID КОДОВЕ

Този тип регистър на данни включва идентификационния код, както и ревизионния номер на устройството. Така че тези данни позволяват на устройството да бъде свързано към неговия BSDL (Boundary Scan Description Language) файл. Този файл включва подробности за конфигурацията на граничното сканиране за устройството.

Работата на JTAG първоначално се избира в режим на инструкция, където едно от състоянията в този режим „път“ позволява на оператора да часовник в рамките на инструкция от TDI. След това държавната машина се развива, докато се пренареди. Следващата стъпка за повечето инструкции е да изберете режим на данни. Така че в този режим данните се зареждат през TDI за четене от TDO. За TDI & TDO пътеките на данните ще бъдат подредени в съответствие с инструкцията, която е записана. След като операцията за четене/запис е извършена, машината на състоянието отново се развива до състояние на нулиране.

Разлика между JTAG срещу UART

Разликата между JTAG и UART включва следното.

| JTAG |

UART |

| Терминът „JTAG“ означава Joint Test Action Group. | Терминът „ UART ” означава Универсален асинхронен приемник/предавател. |

| Това е синхронен интерфейс, който използва вграден хардуер за програмиране на светкавицата . | UART е асинхронен интерфейс, който използва буутлоудър, който работи в паметта. |

| Това е набор от тестови портове, които се използват за отстраняване на грешки, но могат да се използват и за програмиране на фърмуер (което обикновено се прави).

|

UART е вид чип, който контролира комуникациите към и от устройство, като микроконтролер, ROM, RAM и т.н. През повечето време това е серийна връзка, която ни позволява да комуникираме с устройство. |

| Предлагат се в четири типа TDI, TDO, TCK, TMS и TRST. | Те се предлагат в два типа глупав UART и FIFO UART. |

| Joint Test Action Group е серийно програмиране или протокол за достъп до данни, който се използва при взаимодействието на микроконтролери и свързани устройства. | UART е един вид чип, иначе подкомпонент на микроконтролера, който се използва за осигуряване на хардуера за генериране на асинхронен сериен поток като RS-232/RS-485. |

| JTAG компонентите са процесори, FPGA, CPLDs , и т.н. | Компонентите на UART са CLK генератор, I/O регистри за изместване, буфери за предаване или получаване, буфер на шина за системни данни, контролна логика за четене или запис и др. |

JTAG анализатор на протоколи

JTAG анализатор на протоколи като PGY-JTAG-EX-PD е един вид анализатор на протоколи, включващ някои функции за улавяне и отстраняване на грешки в комуникацията между хоста и тествания дизайн. Този тип анализатор е водещият инструмент, който позволява на инженерите по тестване и проектиране да тестват конкретните дизайни на JTAG за неговите спецификации чрез подреждане на PGY-JTAG-EX-PD като Master или Slave за генериране на JTAG трафик и декодиране на декодиращите пакети на Протокол на групата за съвместно изпитване.

Характеристика

Характеристиките на анализатора на протокол JTAG включват следното.

- Поддържа до 25 MH JTAG честоти.

- Той генерира JTAG трафик и декодиране на протокол за шината едновременно.

- Има JTAG Master Capability.

- Променливи JTAG скорости на данни и работен цикъл.

- Дефинирани от потребителя закъснения на TDI и TCK.

- Хост компютър USB 2.0 или 3.0 интерфейс.

- Анализ на грешки в декодирането на протокола

- Протоколно декодирана времева диаграма на шината.

- Непрекъснато поточно предаване на данни от протокола към хост компютъра за осигуряване на голям буфер.

- Списък с дейности по протокол.

- При различни скорости може да се напише скрипт за упражнение за комбиниране на генериране на множество кадри с данни.

Времева диаграма

The времева диаграма на JTAG протоколът е показан по-долу. В следващата диаграма щифтът TDO остава в условията на висок импеданс, освен по време на състояние на контролера за превключване на IR/изместване на DR.

В условията на контролера shift-IR & Shift-DR, щифтът TDO се актуализира на намаляващия ръб на TCK през Target и се взема проби на нарастващия ръб на TCK през хоста.

И двата TDI и TMS щифта просто се вземат проби от нарастващия ръб на TCK чрез Target. Актуализиран на намаляващия ръб, в противен случай TCK през хост.

Приложения

The JTAG приложения включват следното.

- Joint Test Action Group често се използва в процесорите за предоставяне на правото на достъп до техните функции за емулация или отстраняване на грешки.

- Всички CPLD и FPGA използват това като интерфейс за предоставяне на достъп до техните функции за програмиране.

- Използва се за тестване на печатни платки без физически достъп

- Използва се за производствени тестове на ниво платка.

И така, това е всичко преглед на JTAG – pin конфигурация, работа с приложения. Индустриалният стандарт JTAG се използва за проверка на дизайна, както и за тестване на печатни платки след производството. Ето един въпрос към вас, JTAG означава?