Два основни типа БНТ, които съществуват в момента, са: JFET и MOSFET.

MOSFET-овете могат допълнително да бъдат класифицирани по тип на изчерпване и тип подобрение. И двата типа определят основния режим на работа на MOSFET, докато самият термин MOSFET е съкращението на транзистор с ефект на метал-оксид-полупроводник-поле.

Поради факта, че двата типа имат различни работни характеристики, ще оценяваме всеки от тях поотделно в различни статии.

Разлика между MOSFET за подобрение и изчерпване

По принцип, за разлика от подобряващите MOSFET-та, изчерпването на MOSFET-ите е в състояние дори при наличие на 0 V през терминалите от порта към източника (VGS).

За подобряване на MOSFET напрежението от порта към източника (VGS) трябва да бъде над прага на напрежението от вход към източник (VGS (th)) за да го накара да поведе .

За MOSFET с изчерпване на N-канал обаче стойността на VGS (th) е над 0 V. Това означава, че дори VGS = 0 V, MOSFET с изчерпване е в състояние да проведе ток. За да го изключите, VGS на изчерпващия MOSFET трябва да бъде намален под VGS (th) (отрицателен).

В настоящата статия ще обсъдим типа изчерпване MOSFET, за който се твърди, че има характеристики, съвпадащи с тези на JFET. Приликата е между границата и наситеността близо до IDSS.

Основна конструкция

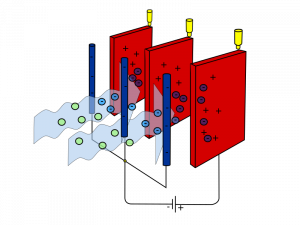

Фиг. 5.23 показва основната вътрешна структура на MOSFET от тип изчерпване на n-канал.

Можем да намерим блок от p-тип материал, създаден с помощта на силициева основа. Този блок се нарича субстрат.

Основата е основата или основата, върху която е изграден MOSFET. За някои MOSFET транзистори той е вътрешно свързан с терминала „източник“. Също така много устройства предлагат допълнителен изход под формата на SS, с 4-терминален MOSFET, както е показано на фиг. 5.23

Клемите за източване и източника са свързани чрез проводящи контакти към допирани места и прикрепени през n-канал, както е посочено на същата фигура.

Портата също е свързан с метален слой, въпреки че е изолиран от n-канала чрез фин слой силициев диоксид (SiOдве).

SiOдвепритежава уникална форма на изолационно свойство, наречено диелектрик, което създава противоположно електрическо поле в себе си в отговор на външно приложено електрическо поле.

Като изолационен слой, материалът SiOдвени предлага следната важна информация:

С този материал е разработена пълна изолация между терминала на портата и канала на MOSFET.

Нещо повече, това е заради SiOдве, портата на MOSFET е в състояние да се отличава с изключително висока степен на входен импеданс.

Поради това жизненоважно високо входно импедансно свойство, токът на затвора IGе практически нула усилватели за всяка конфигурация на MOSFET с постоянен ток.

Основни операции и характеристики

Както може да се види на фиг. 5.24, напрежението на порта към източника е конфигурирано на нула волта чрез свързване на двата терминала заедно, докато напрежение VDSсе прилага през клемите за източване и източник.

С горната настройка, източващата страна установява положителен потенциал от n-каналните свободни електрони, заедно с еквивалентен ток през JFET канала. Също така полученият ток VGS= 0V все още се идентифицира като IDSS, както е дадено на фиг. 5.25

Виждаме, че на фиг. 5.26 напрежението на източника на порта VGSсе дава отрицателен потенциал под формата на -1V.

Този отрицателен потенциал се опитва да принуди електроните към субстрата на р-канала (тъй като зарядите се отблъскват) и да изтегли дупки от субстрата на р-канала (тъй като противоположните заряди се привличат).

В зависимост от това колко голямо е това отрицателно пристрастие VGSсе извършва рекомбинация на дупки и електрони, което води до намаляване на свободните електрони в n-канала, наличен за проводимостта. По-високите нива на отрицателно отклонение водят до по-висок процент на рекомбинация.

Следователно токът на източване се намалява, тъй като горното условие на отрицателно отклонение се увеличава, което е доказано на фиг. 5.25 за VGSнива на VGS= -1, -2 и т.н., докато маркировката за откъсване на -6V.

Токът на изтичане в резултат заедно с графиката на трансферната крива протича точно като този на a JFET.

Сега, за положителното VGSСтойностите на портата ще привличат излишните електрони (свободни носители) от p-тип подложка, поради обратния ток на изтичане. Това ще установи нови носители по пътя на резултатни сблъсъци между ускоряващите се частици.

Тъй като напрежението от порта към източника има тенденция да се повишава с положителна скорост, токът на източване показва бързо нарастване, както е доказано на фиг. 5.25 по същите причини, както беше обсъдено по-горе.

Разликата се разви между кривите на VGS= 0V и VGS= +1 ясно показва сумата, с която токът се е увеличил поради вариацията на V на 1 VGS

Поради бързото покачване на източващия ток трябва да внимаваме за максималния ток, в противен случай той може да премине положителната граница на напрежението на портата.

Например за типа устройство, изобразен на фиг. 5.25, се прилага VGS= + 4V би причинило изтичането на ток да се повиши при 22,2 mA, което може да пресича максималната граница на пробив (ток) на устройството.

Горното условие показва, че използването на положително напрежение врата-източник генерира засилен ефект върху количеството на свободните носители в канала, за разлика от когато VGS= 0V.

Ето защо областта на положителното напрежение на затвора на характеристиките на дренаж или трансфер е известна като регион за подобрение . Тази област се намира между границата и нивото на насищане на IDSSили региона на изчерпване.

Решаване на примерен проблем

Предимства и приложения

За разлика от MOSFET в режим на подобрение, където откриваме, че изтичащият ток пада до нула в отговор на нулево напрежение от порта към източника, съвременният FET в режим на изчерпване има забележим ток с нулево напрежение на затвора. За да бъдем точни, съпротивлението източване към източник обикновено е 100 ома при нулево напрежение.

Както е посочено в горната графика, RDS на съпротивлението ON(На)спрямо аналоговия обхват на сигнала изглежда като практически плосък отговор. Тази характеристика, заедно с ниските нива на капацитет на тези усъвършенствани устройства с изчерпване, им позволяват да бъдат особено идеални като аналогови превключватели за приложения за превключване на аудио и видео.

Атрибутът 'нормално включен' на MOSFET в режим на изчерпване позволява на устройството да бъде напълно подходящо за единични регулатори на ток на FET.

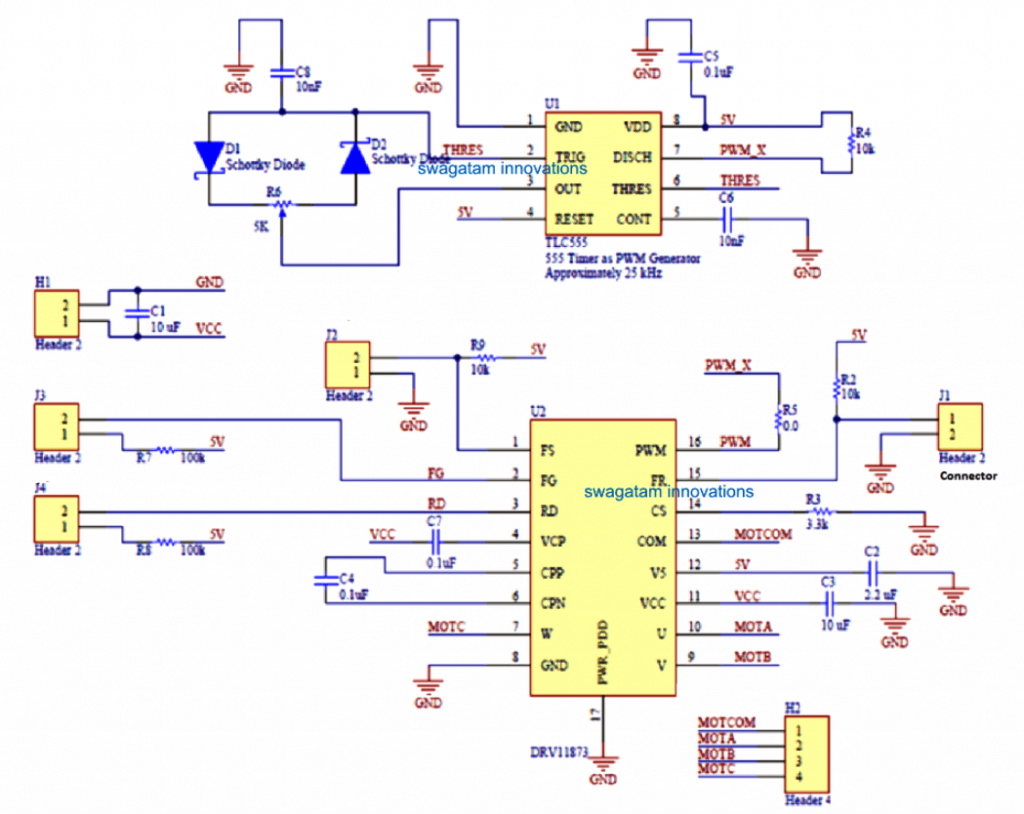

Една такава примерна схема може да се види на следващата фигура.

Стойността на Rs може да се определи по формулата:

Rс= VGSизключен[1 - (Iд/ IDSS)1/2] / Iд

където Азд е количеството регулиран ток, необходимо на изхода.

Основното предимство на MOSFET в режим на изчерпване в приложението с токов източник е техният минимален капацитет на източване, което ги прави подходящи за отклоняващи приложения в схеми с ниско входно изтичане, средни скорости (> 50 V / us).

Фигурата по-долу показва диференциал на тока с нисък входящ ток от предния край, използващ двойна функция за ниско изтичане FET.

Най-общо казано, двете страни на JFET ще бъдат пристрастни при ID = 500 uA. Следователно, токът, който може да се получи за компенсация на зареждане и разсеяни капацитети, се ограничава до 2ID или, в случаи като този, 1,0 mA. Съответните характеристики на JFET са доказани от производството и са гарантирани в листа с данни.

Cs символизира изходния капацитет на източника на ток на 'опашката' на входния етап. Този капацитет е от решаващо значение при неинвертиращите усилватели, поради факта, че входният етап изпитва значителен обмен на сигнали в цялата мрежа и зарядните токове в Cs могат да бъдат големи. В случай, че се използват нормални източници на ток, този капацитет на опашката може да бъде отговорен за забележимо влошаване на скоростта на нарастване в неинвертиращите вериги (в сравнение с инвертиращите приложения, където зарядните токове в Cs са склонни да бъдат минимални).

Спадът в скоростта на убиване може да се изрази като:

1/1+ (Cs / Sc)

Докато Cs е по-нисък от Cc (компенсаторният кондензатор), може да има едва ли не някакви вариации в скоростта на нарастване. Работейки с DMOS FET, Cs могат да бъдат около 2 pF. Тази стратегия води до значително подобрение в скоростта на убиване. Когато са необходими текущи дефицити, по-високи от 1 до 5 mA, устройството може да бъде сместено в режим на подобрение, за да генерира до 20 mA за максимален VGS от +2,5 V, като минималният изходен капацитет продължава да бъде ключов аспект.

Следващото приложение по-долу показва подходяща верига на източника на ток в режим на подобрение.

Аналогов превключвател „нормално включен“ може да бъде изграден за изисквания, при които се налага стандартно състояние по време на неизправност на захранващото напрежение, например при автоматично определяне на диапазона на тестовите инструменти или за осигуряване на точно стартиране на логическите вериги при включен ключ.

Намаленото отрицателно прагово напрежение на устройството предлага основни предпоставки за задвижване и позволява работа с минимално напрежение.

Схемата по-долу показва общите фактори на пристрастие за всеки аналогов превключвател DMOS в режим на изчерпване.

За да се изключи устройството, на портата се налага отрицателно напрежение. Като се има предвид това, съпротивлението при включване може да бъде сведено до минимум, когато FET допълнително се усили, използвайки положително напрежение на затвора, което го позволява по-специално в областта на режима на подобрение заедно с региона на изчерпване.

Този отговор може да се види в следващата графика.

Високочестотното усилване на устройството, заедно с неговите ниски стойности на капацитета, осигуряват повишена „стойност на заслугите“. Това наистина е ключов елемент във VHF и UHF усилването, който определя продукта на честотната лента на усилване (GBW) на FET, който може да бъде изобразен като:

GBW = gfs / 2 Пи (° Св+ Cнавън)

p-канал MOSFET тип изчерпване

Конструкцията на p-канален MOSFET тип изчерпване е перфектна обратна страна на n-канална версия, показана на фиг. 5.23. Това означава, че субстратът сега приема формата на n-тип и каналът става p-тип, както може да се види на фиг. 5.28а по-долу.

Идентификацията на терминала остава непроменена, но напрежението и токовите полярности се обръщат, както е посочено на същата фигура. Характеристиките на изтичането ще бъдат точно както е показано на фиг. 5.25, с изключение на VDSзнак, който в този случай ще получи отрицателна стойност.

Токът на източване Iдпоказва положителна полярност и в този случай, защото вече сме обърнали посоката му. VGSпоказва противоположна полярност, което е разбираемо, както е показано на фиг. 5.28в.

Защото VGSе обърната, произвежда огледално изображение за трансферните характеристики, както е показано на Фиг. 5,28b.

Това означава, че изтичащият ток се увеличава в положителното VGSрегион от граничната точка при VGS= Vp, докато IDSS, след това продължава да нараства като отрицателна стойност на VGSсе издига.

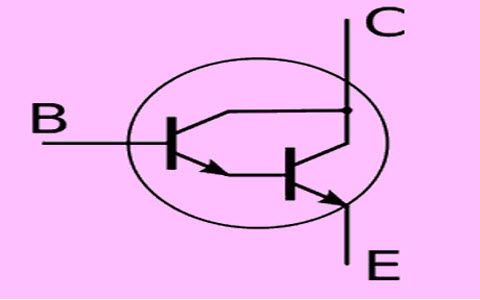

Символи

Графичните знаци за MOSFET тип на изчерпване на n- и p-канал могат да бъдат видени на горната фигура 5.29.

Наблюдавайте начина, по който избраните символи имат за цел да представят истинската структура на устройството.

Липсата на директна взаимосвързаност (поради изолацията на портата) между портата и канала се символизира от пролука между портата и различните клеми на символа.

Вертикалната линия, която представлява канала, е прикрепена между канализацията и източника и е „задържана“ от основата.

На фигурата по-горе са представени две групи символи за всеки тип канал, за да се подчертае фактът, че при някои устройства субстратът може да бъде достъпен отвън, докато при други това може да не се вижда.

MOSFET (тип подобрение)

Въпреки че MOSFET-ите с изчерпване и подобряване изглеждат сходни с вътрешните си структури и функционален режим, техните характеристики могат да бъдат доста различни.

Основната разлика е в източващия ток, който зависи от конкретно ниво на напрежение от врата към източник за прекъсването.

По-точно, MOSFET от подобрен тип от n-канал може да работи с положително напрежение порта / източник, вместо диапазон от отрицателни потенциали, които обикновено могат да повлияят на MOSFET тип изчерпване.

Основна конструкция

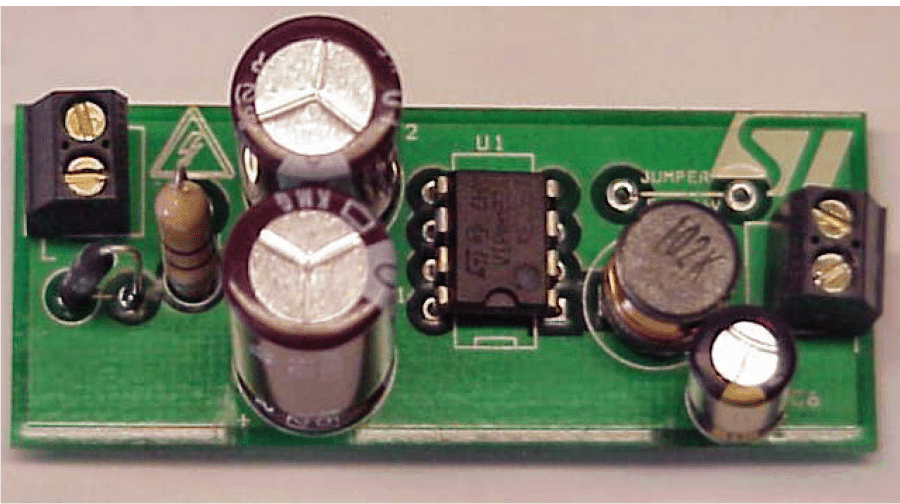

Можете да визуализирате MOSFET тип подобрение от n-канал по-долу

Фиг. 5.31.

Секция от материал тип p се създава чрез силициева основа и както е научено преди това се нарича субстрат.

Този субстрат в някои случаи е прикрепен вътрешно към изходния щифт в MOSFET с изчерпване, докато в някои случаи той е прекратен като четвърти проводник, за да позволи външен контрол на потенциалното му ниво.

Клемите за източник и източване се свързват както обикновено с помощта на метални контакти към допирани области.

Може обаче да е важно да се визуализира, че на фиг. 5.31 липсва каналът между двата допирани n области.

Това може да се разглежда като основно различие между вътрешното оформление на MOSFET от тип изчерпване и подобрение, което е отсъствие на присъщ канал, който се предполага, че е част от устройството.

Слоят SiO2 може да се види все още преобладаващ, което осигурява изолация между металната основа на терминала на портата и областта между канализацията и източника. Тук обаче може да се види, че стои отделено от секцията за материали от тип p.

От горната дискусия можем да заключим, че вътрешното оформление на MOSFET за изчерпване и подобряване може да има някои прилики, с изключение на липсващия канал между източване / източник за тип подобрение на MOSFET.

Основни операции и характеристики

За тип подобрение MOSFET, когато 0 V се въведе в неговата VGS, поради липсващия n-канал (за който е известно, че носи много свободни носители) причинява токов изход да бъде нула, което е доста различно от типа на изчерпване на MOSFET, с ID = IDSS.

В такава ситуация поради липсващ път през терминалите за източване / източник, големи количества носители под формата на електрони не могат да се натрупват при източване / източник (поради допираните с n области).

Прилагайки някакъв положителен потенциал при VDS, с VGS, зададен на нула волта и SS терминала, късо с терминала на източника, ние всъщност намираме няколко обратни пристрастни pn връзки между n-легираните области и p-субстрата, за да осигурим забележимо провеждане през източване към източника.

На фиг. 5.32 е показано състояние, при което VDS и VGS се прилагат с някакво положително напрежение, по-високо от 0 V, което позволява дренажът и затворът да имат положителен потенциал по отношение на източника.

Положителният потенциал на затвора изтласква отворите в p-субстрата по ръба на SiO2 слоя, напускащ мястото и навлизайки по-дълбоко в областите на p-субстрата, както е показано на горната фигура. Това се случва поради подобни обвинения, които се отблъскват.

Това води до създаване на област на изчерпване близо до изолационния слой SiO2, който е без дупки.

Въпреки това p-субстратните електрони, които са малцинствените носители на материала, се изтеглят към положителната порта и започват да се събират в района близо до повърхността на SiO2 слоя.

Поради изолационното свойство на слоя SiO2 отрицателните носители позволяват на отрицателните носители да се абсорбират в терминала на портата.

Тъй като увеличаваме нивото на VGS, електронната плътност близо до повърхността на SiO2 също се увеличава, докато накрая индуцираната област от n-тип е в състояние да позволи количествено измерима проводимост през дренаж / източник.

Величината на VGS, която причинява оптимално увеличаване на източващия ток, се нарича прагово напрежение, означено със символа VT . В таблиците с данни ще можете да видите това като VGS (Th).

Както се научих по-горе, поради липсата на канал при VGS = 0 и „подобрен“ с положителното приложение на напрежението от порта към източника, този тип MOSFET са известни като MOSFET от подобрен тип.

Ще откриете, че MOSFET-овете с изчерпване и подобрение показват региони от тип подобрение, но терминът подобрение се използва за последния, тъй като той специално работи, като използва подобрен режим на работа.

Сега, когато VGS бъде изтласкана над праговата стойност, концентрацията на свободните носители ще се увеличи в канала, където е индуцирана. Това води до увеличаване на изтичащия ток.

От друга страна, ако поддържаме VGS постоянен и повишим нивото на VDS (напрежение от източник към източник), това в крайна сметка ще доведе до достигане на точката на насищане на MOSFET, както обикновено се случва с всеки JFET или MOSFET с изчерпване.

Както е показано на фиг. 5.33, идентификационният ток на изтичащия ток се изравнява с помощта на процес на притискане, посочен от по-тесния канал към източващия край на индуцирания канал.

Чрез прилагане на закона за напрежението на Kirchhoff към крайните напрежения на MOSFET на фиг. 5.33, получаваме:

Ако VGS се поддържа постоянна до определена стойност, например 8 V, и VDS се повиши от 2 до 5 V, напрежението VDG от уравнение 5.11 може да се види, че пада от -6 на -3 V и потенциалът на затвора става все по-малко положителен по отношение на източващото напрежение.

Този отговор забранява на свободните носители или електрони да се изтеглят към тази област на индуцирания канал, което от своя страна води до спад в ефективната ширина на канала.

В крайна сметка ширината на канала намалява до точката на откъсване, достигайки състояние на насищане, подобно на това, което вече научихме в нашата по-ранна статия за изчерпване на MOSFET.

Това означава, че увеличаването на VDS допълнително с фиксиран VGS не влияе на нивото на насищане на ID, докато достигне точката, в която се стигне до повреда.

Разглеждайки фигура 5.34, можем да идентифицираме, че за MOSFET, както на фиг. 5.33 с VGS = 8 V, насищането се извършва при ниво на VDS от 6 V. За да бъдем точни, нивото на насищане на VDS се свързва с приложеното ниво на VGS чрез:

Без съмнение това означава, че когато стойността на VT е фиксирана, увеличаването на нивото на VGS пропорционално ще доведе до по-високи нива на насищане за VDS чрез локуса на нивата на насищане.

Позовавайки се на характеристиките, показани на горната фигура, нивото на VT е 2 V, което се вижда от факта, че източният ток е спаднал до 0 mA.

Затова обикновено можем да кажем:

Когато стойностите на VGS са по-ниски от праговото ниво за MOSFET от подобрен тип, токът му на източване е 0 mA.

Също така можем ясно да видим на горната фигура, че докато VGS се повдигне по-високо от VT на 8 V, съответното ниво на насищане за ID също се увеличава от 0 до 10 mA ниво.

Освен това можем по-нататък да забележим, че пространството между нивата на VGS се увеличава с увеличаване на стойността на VGS, причинявайки безкрайно нарастващи стъпки в източващия ток.

Откриваме, че стойността на тока на източване е свързана с напрежението от порта към източника за нива на VGS, което е по-голямо от VT, чрез следната нелинейна връзка:

Терминът, който е показан в квадратна скоба, е терминът, който е отговорен за нелинейната връзка между ID и VGS.

Терминът k е константа и е функция от оформлението на MOSFET.

Можем да разберем стойността на тази константа k чрез следното уравнение:

където ID (включен) и VGD (включен) са стойности, специфично в зависимост от характеристиката на устройството.

На следващата фиг. 5.35 по-долу откриваме, че характеристиките за източване и прехвърляне са разположени една до друга, за да изяснят процеса на прехвърляне един върху друг.

По принцип той е подобен на процеса, обяснен по-рано за JFET и MOSFET от тип изчерпване.

За настоящия случай обаче трябва да помним, че източният ток е 0 mA за VGS VT.

Тук ID може да види забележимо количество ток, което ще се увеличи, както е определено от уравнение. 5.13.

Имайте предвид, че докато дефинираме точките върху характеристиките на прехвърляне от характеристиките на източване, ние вземаме предвид само нивата на насищане. Това ограничава района на работа до VDS стойности, по-високи от нивата на насищане, установени от уравнение. (5.12).

p-канални MOSFET от тип подобрение

Структурата на MOSFET от тип подобрение на p-канал, както е показано на фиг. 5.37а, е точно обратната на тази, показана на фиг. 5.31.

Значение, сега откривате, че субстрат от n-тип и р-легирани области под дренажните и източните съединения.

Клемите продължават да бъдат както е установено, но всяка от текущите посоки и полярностите на напрежението са обърнати.

Характеристиките на изтичане могат да изглеждат така, както са дадени на фиг. 5.37в, като имат нарастващи количества ток, причинени от непрекъснато по-отрицателни величини на VGS.

Характеристиките на трансфера биха били огледалното впечатление (около оста ID) на кривата на трансфер от фиг. 5.35, като ID се увеличава с все повече и повече отрицателни стойности на VGS над VT, както е показано на фиг. 5.37b. Уравненията (5.11) до (5.14) са също толкова подходящи за p-каналните устройства.

Препратки:

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

Предишна: Верига на анти шпионски RF детектор - Безжичен детектор на грешки Напред: Характеристики на прехвърляне