Постът обсъжда функцията за пиноут и други важни спецификации на IC 4043. Нека научим за пълния лист с данни на този много интересен чип.

Лист с данни за разпитване на IC 4043

Технически IC 4043 е ключалка за задаване / нулиране (R / S) с 3 логически изходни състояния.

За да бъдем по-точни, този чип има 4 комплекта входове (което означава 8 входни пинота) и 4 съответни единични изхода.

4-те комплекта входове се състоят от 4 двойки входове за настройка / нулиране.

За всеки набор / нулиране имаме един съответстващ изход.

Всички тези зададени нулиращи входове реагират на високи логически сигнали, създавайки бистабилен ефект при съответните им изходни изводи.

Бистабилно флип / флоп

Бистабилът се отнася до действие на флип флоп, с други думи, високият импулс към входа „set“ прави съответния изход висок от първоначалното си ниско състояние, а високият към нулирания вход връща горното състояние от високо обратно в ниско състояние.

Следователно основно, за да направим съответните изходи високи, трябва да приложим високо на техните „зададени“ входове и за да направим изходите отново ниски, просто трябва да приложим още едно високо към техните нулирани входове.

Функционирането на входните и изходните изводи е толкова просто.

В допълнение към това, ИС има още едно интересно OE входно пино, което е често срещано изходно пино.

Функция за задаване / нулиране

За да разрешите описаните по-горе действия за настройка / нулиране в интегралната схема, този OE вход трябва да бъде свързан с висока логика или просто с Vdd (захранващо напрежение).

В горната ситуация изходът е разрешен с посоченото функциониране на тригер.

Ако входът на OE е свързан със земя, изходът замръзва и произвежда отклик с висок импеданс, който не показва нито нисък изход, нито висок, а заключва входа на блокиращо състояние, което не реагира, оттук и името 3 логически изход.

По този начин OE входът може да се използва за изключване на функционирането на интегралната схема, ако е необходимо за конкретно приложение.

IC работи най-добре с захранващи напрежения от 5 до 15V.

Нека обобщим входящите изходни функции и спецификации на IC 4043 със следните данни:

- 1Q до 4Q (изводи: 2, 9, 10, 1) изход за буфериране с 3 състояния

- 1R до 4R (щифтове: 3, 7, 11, 15) вход за нулиране (активен HIGH)

- 1S до 4S (щифтове: 4, 6, 12, 14) задайте вход (активен HIGH)

- OE (Pin: 5) общ изход позволява вход

- VSS (Pin: 8) захранващо напрежение на земята

- NC (Pin: 13) не е свързан

- VDD (Pin: 16) захранващо напрежение

Още актуализации:

В тази публикация ние се опитваме да разберем работата на IC 4043 и IC 4044, като изучаваме различните спецификации, технически лист на устройствата и тяхното подреждане.

По принцип и двата варианта са с четири кръстосано свързани CMOS 3-държавни R / S или Reset / Set Latches. Quad означава да има 4 изхода, които могат да бъдат настроени или фиксирани с висока логика чрез управляващ входен сигнал или да бъдат върнати на нула на логиката чрез последващ входен сигнал.

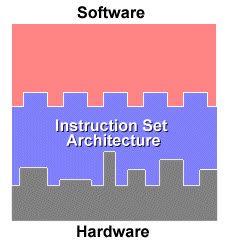

Функцията с 3 състояния позволява интегралните схеми да се управляват с помощта на 3 логика

Основният принцип на работа на IC 4043 и IC 4044 е същият, както по-горе, като единствената разлика е, че IC 4043B са четиристепенно кръстосано свързани 3 състояния НИТО Latch и IC 4044B са четворно кръстосано свързани 3 състояния NAND Резе.

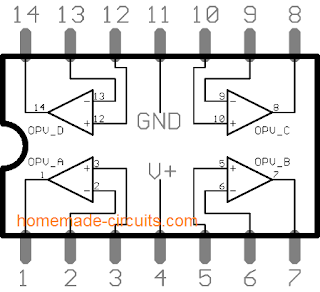

Диаграма на пиноут

Следните диаграми на пиновете на интегралните схеми показват вътрешната структура и подробности за пиновете на устройствата:

На диаграмите по-горе можем да видим, че всеки от типовете има 4 ключалки с един изход и 2 отделни входа RESET / SET. Функцията на щифта ENABLE за всички входове SET / RESET е идентична.

Логиката HIGH на щифта ENABLE позволява на състоянията на резето да се свържат със съответните изходи, а логиката ниска или 0 изключва състоянията на резетата от техните изходи, причинявайки пълна отворена верига през изходите.

NOR Latch, NAND Latch еквивалентни логически диаграми

Следващите диаграми показват еквивалентните резета под формата на NOR и NAND резета, които се намират във всеки от 4-те резета на отделните интегрални схеми.

Както виждаме, всеки от блокиращите блокове се управлява с помощта на 3 логически контролни входа, а именно SET, RESET и ENABLE, следователно изходът зависи от тези 3 състояния на вход. Таблицата на истината за тези 3 логически състояния може да се научи от следната диаграма:

В горната таблица на истината, пълната форма на различните съкратени символни азбуки може да се разбере, както е дадено по-долу: S = ПИН ПИН = НУЛИРАН ПИН Е = РАЗРЕШИ ПИН Q = ИЗХОД ПИН OC = Отворена верига NC = Без промяна

Основните характеристики на IC 4043 и IC 4044 са обобщени по-долу:

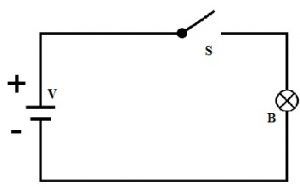

Практическа основна симулация на работа на щифтовете SET / RESET и ENABLE

Работно описание

От горния симулационен GIF можем да разберем работата на четириядрените модули със заключване със следните точки:

Когато SET е приложен с положително захранване, изходът става висок и се фиксира, дори ако положителният потенциал е отстранен от SET щифта, както е показано от червения светодиод (пристрастен напред).

Когато RESET щифтът се приложи с положителен импулс, резето се счупва и изходът отива LOW за постоянно, дори ако позитивът е отстранен от RESET щифта. Това се показва от осветяването на синия светодиод.

Горните операции могат да бъдат приложени само дотогава, докато щифтът ENABLE на IC е с положителен потенциал за доставка. Когато е прикрепен към отрицателен или заземен потенциал, изходът на резето става отворен и не реагира на операциите SET / RESET.

Предишна: Програмируем таймер на седмица ден Напред: IC 4033 Pinouts, Datasheet, Application