Различни видове цифрови системи са изградени от много малко видове основни мрежови конфигурации като AND порта, NAND порта, или порта и т.н. ... Тези елементарни вериги се използват отново и отново в различни топологични комбинации. В допълнение към логиката, цифровите системи трябва да съхраняват и двоични числа. За тези клетки на паметта, известни също като FLIP-FLOP ’ са проектирани. За изпълнение на някои функции като двоично добавяне. Следователно, за изпълнение на такива функции, комбинации от логически порти и FLIP-FLOP са проектирани върху едночипова интегрална схема. Тези интегрални схеми представляват практически градивни елементи на цифровите системи. Един от тези градивни елементи, използвани за двоично добавяне, е Carry Look-forward Adder.

Какво е Carry Look-Adder?

Цифровият компютър трябва да съдържа схеми, които могат да извършват аритметични операции като събиране, изваждане, умножение и деление. Сред тях събирането и изваждането са основните операции, докато умножението и делението са съответно повторното събиране и изваждане.

За извършване на тези операции се прилагат „Adder схеми“ с помощта на основни логически порти. Съединителни вериги са еволюирали като полусъбирач, пълен суматор, разпръскващо пренасяне и пренасяне на поглед напред-назад.

Сред тези Carry Look-forward Adder е по-бързата верига на суматора. Той намалява забавянето на разпространението, което възниква по време на добавянето, чрез използване на по-сложни хардуерни схеми. Проектиран е чрез трансформиране на веригата за пренасяне на пулсации, така че логиката на пренасяне на суматора да се промени в логика на две нива.

4-битово пренасяне с перспектива за добавяне

При паралелните суматори износът на всеки пълен суматор се дава като пренос на вход към следващото състояние от по-висок ред. Следователно, тези суматори не е възможно да произвеждат изходи за пренасяне и сумиране на което и да е състояние, освен ако за това състояние няма наличен вход за пренасяне.

Така че, за да се получи изчислението, веригата трябва да изчака, докато битът за пренасяне се разпространи във всички състояния. Това предизвиква забавяне на разпространението във веригата.

4-битов Ripple-Carry-Adder

Помислете за 4-битовата схема за добавяне на пулсации по-горе. Тук сумата S3 може да бъде получена веднага след като бъдат дадени входовете A3 и B3. Но пренасянето C3 не може да се изчисли, докато не се приложи бит за пренасяне C2, докато C2 зависи от C1. Следователно, за да се получат окончателни резултати в стабилно състояние, преносът трябва да се разпространява през всички състояния. Това увеличава забавянето на разпространението на веригата.

Забавянето на разпространението на суматора се изчислява като „забавяне на разпространението на всяка порта, умножено по броя на етапите във веригата“. За изчисляването на голям брой битове трябва да се добавят още етапи, което прави забавянето много по-лошо. Следователно, за да се реши тази ситуация, беше представен Carry Look-forward Adder.

За да се разбере функционирането на Carry Look-forward Adder, по-долу е описан 4-битов Carry Look-forward Adder.

4-битова диаграма за носене-поглед-напред-добавяне-логика

В този суматор входът за пренасяне на всеки етап от суматора е независим от носещите битове, генерирани на независимите етапи. Тук изходът на който и да е етап зависи само от битовете, които са добавени в предишните етапи, и входящия вход, предоставен в началния етап. Следователно, веригата на всеки етап не трябва да чака генерирането на бит за носене от предишния етап и бит за носене може да бъде оценен по всяко време.

Таблица на истината на Carry Look-Adder

За извличане на таблицата на истината на този суматор се въвеждат два нови термина - Carry генериране и пренасяне на разпространение. Носете генериране на Gi = 1, когато се генерира пренос Ci + 1. Зависи от входовете Ai и Bi. Gi е 1, когато Ai и Bi са 1. Следователно Gi се изчислява като Gi = Ai. Би.

Носенето, разпространено Pi, е свързано с разпространението на пренасяне от Ci до Ci + 1. Изчислява се като Pi = Ai ⊕ Bi. Таблицата на истината на този суматор може да бъде получена от модифицирането на таблицата на истината на пълен суматор.

Използвайки термините Gi и Pi, сумите Si и Carry Ci + 1 са дадени както по-долу -

- Si = Pi ⊕ Gi.

- Ci + 1 = Ci.Pi + Gi.

Следователно носещите битове C1, C2, C3 и C4 могат да бъдат изчислени като

- C1 = C0.P0 + G0.

- C2 = C1.P1 + G1 = (C0.P0 + G0) .P1 + G1.

- C3 = C2.P2 + G2 = (C1.P1 + G1) .P2 + G2.

- C4 = C3.P3+G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3.

Може да се наблюдава от уравненията, които носят Ci + 1, зависи само от носенето C0, а не от междинните носещи битове.

Носете поглед-напред-добавяне-таблица на истината

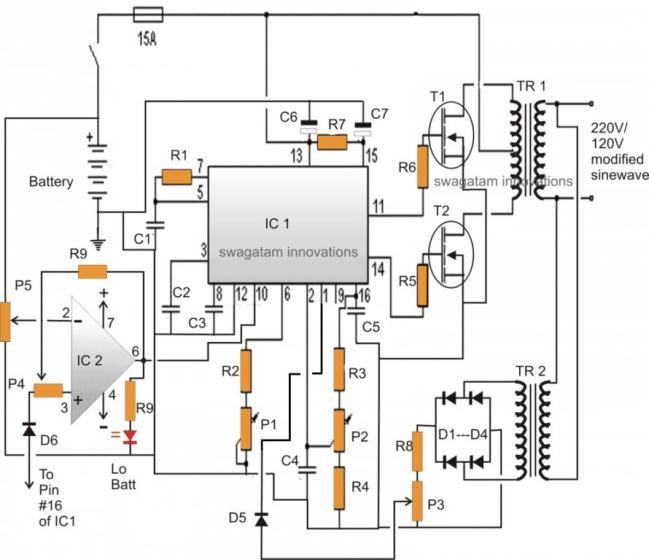

Електрическа схема

Горните уравнения се изпълняват с помощта на двустепенни комбинационни вериги заедно с И, ИЛИ портали, където се приема, че портата има множество входове.

Carry-Output-Generation-Circuit-of-Carry-Look-forward-Adder

Веригата Carry Look-forward Adder за 4-битова е дадена по-долу.

4-битова схема за носене-поглед-напред-добавяне-схема

8-битовите и 16-битовите схеми за пренасяне на поглед напред-назад могат да бъдат проектирани чрез каскадиране на 4-битовата сумационна верига с логика за носене.

Предимства на Carry Look-forward Adder

В този суматор забавянето на разпространението се намалява. Изходът за пренасяне на всеки етап зависи само от началния бит за пренасяне на началния етап. С помощта на този суматор е възможно да се изчислят междинните резултати. Този суматор е най-бързият суматор, използван за изчисление.

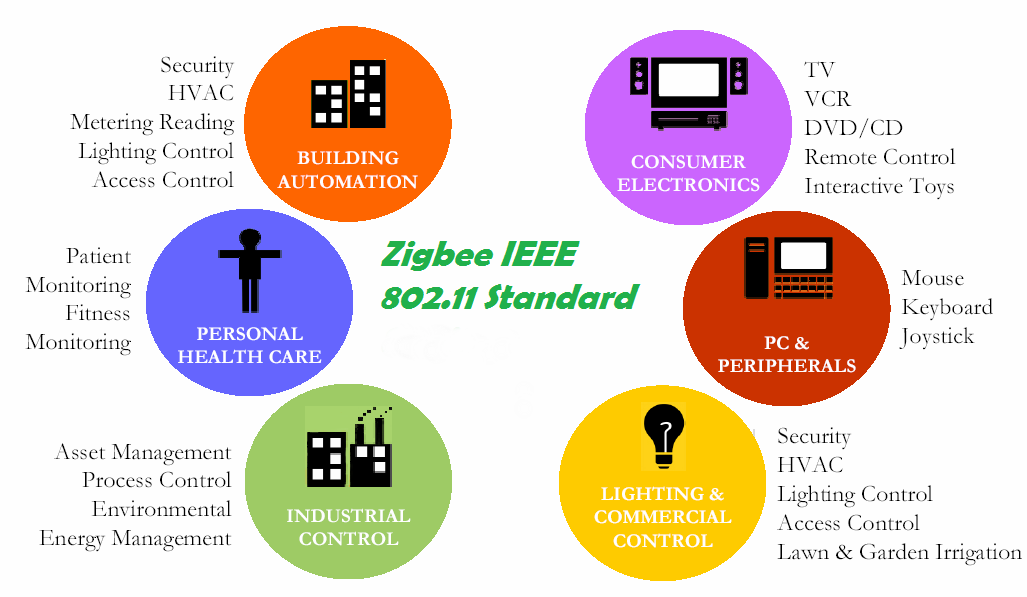

Приложения

Високоскоростните носители за носене с поглед напред се използват, както са внедрени като интегрални схеми. Следователно е лесно да вградите суматора във вериги. Чрез комбиниране на два или повече сумиращи изчисления на по-високи битови булеви функции може да се направи лесно. Тук увеличението на броя на портите също е умерено, когато се използва за по-високи битове.

За този Adder има компромис между площта и скоростта. Когато се използва за изчисления с по-висок бит, той осигурява висока скорост, но сложността на веригата също се увеличава, като по този начин се увеличава площта, заета от веригата. Този суматор обикновено се изпълнява като 4-битови модули, които се каскадират заедно, когато се използват за по-високи изчисления. Този суматор е по-скъп в сравнение с други суматори.

За булеви изчисления в компютри, суматорите се използват редовно. Чарлз Бабидж внедри механизъм за предвиждане на бита за пренасяне в компютрите, за да намали забавянето, причинено от пулсации за носене . Докато проектирате система, скоростта на изчисление е най-високият решаващ фактор за дизайнера. През 1957 г. Джералд Б. Розенбергер патентова съвременния Bider Carry Look-forward Adder. Въз основа на анализа на закъснението и симулацията на портата се провеждат експерименти за модифициране на веригата на този суматор, за да стане още по-бърза. За n-битово пренасяне с добавка за гледане напред, какво е забавянето на разпространението, когато дадено забавяне на всяка порта е 20?

Кредит за изображение