В комбинационните вериги се използват различни логически порти за проектиране на кодер, мултиплексор, декодер и демултиплексор. Тези схеми имат някои характеристики, като изходът на тази схема зависи главно от нивата, които са по всяко време на входните клеми. Тази схема не включва никаква памет. По-ранното състояние на входа няма влияние върху текущото състояние на тази верига. Входовете и изходите на комбинационна схема са „n“ не. на входовете & ‘m’ бр. на изходите. Някои от комбинационните вериги са наполовина суматор и пълен суматор, субтрактор, енкодер, декодер, мултиплексор и демултиплексор. Тази статия разглежда общ преглед на половината суматор и пълния суматор и работи с таблици за истинност.

Какво е Adder?

Суматорът е a цифрова логическа схема в електрониката, която се използва широко за добавяне на числа. В много компютри и други видове процесори суматорите дори се използват за изчисляване на адреси и свързани дейности и изчисляване на индекси на таблици в ALU и дори се използват в други части на процесорите. Те могат да бъдат изградени за многобройни представления като излишък-3 или двоично кодиран десетичен знак. По принцип добавящите се класифицират в два типа: половин добавяне и пълно добавяне.

Какво представлява веригата за половин и пълна сума?

Веригата на полусумара има два входа: A и B, които добавят две входни цифри и генерират пренос и сума. Схемата на пълния суматор има три входа: A и C, които добавят три входни числа и генерират пренос и сума. Тази статия дава подробна информация за целта на половин суматор и пълен суматор в таблични форми и дори в електрически схеми също. Вече беше споменато, че основната и решаваща цел на суматорите е добавянето. По-долу са подробни теория на половин суматор и пълна суматор.

Основен половин и пълен суматор

Половината добавяне

И така, стигайки до сценария на половината суматор, той добавя две двоични цифри, където входните битове се наричат augend и addend и резултатът ще бъде два изхода, единият е сумата, а другият е carry. За да се извърши операцията по сумиране, XOR се прилага към двата входа, а И порта се прилага към двата входа, за да се произведе пренасяне.

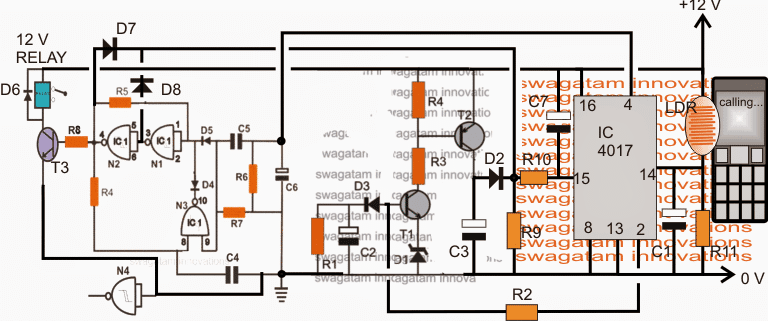

Функционална диаграма на HA

Докато във веригата на пълния суматор той добавя 3 еднобитови числа, където два от трите бита могат да се означават като операнди, а другият се нарича бит, внесен. Полученият изход е 2-битов изход и те могат да бъдат посочени до като изходен носител и сума.

Използвайки половин суматор, можете да проектирате просто добавяне с помощта на логически порти.

Нека да видим пример за добавяне на два единични бита.

2-битовата таблица на истината за половин суматор е както по-долу:

Таблица на истината за половин добавител

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

Това са най-малко възможните еднобитови комбинации. Но резултатът за 1 + 1 е 10, резултатът от сумата трябва да бъде презаписан като 2-битов изход. По този начин уравненията могат да бъдат записани като

0 + 0 = 00

0 + 1 = 01

1 + 0 = 01

1 + 1 = 10

Изходът „1’от„ 10 “е изпълнение. „SUM“ е нормалният изход, а „CARRY“ е изпълнението.

Сега е изяснено, че 1-битов суматор може лесно да бъде реализиран с помощта на XOR Gate за изхода ‘SUM’ и AND Gate за ‘Carry’.

Например, когато трябва да добавим два 8-битови байта заедно, тогава това може да бъде приложено чрез използване на логическа схема с пълен суматор. Полусумарът е полезен, когато искате да добавите една двоична цифра.

Начин за разработване на двубинарни сумиращи цифри би бил да се направи таблица на истината и да се намали. Когато искате да направите три двоичен цифров суматор, операцията за добавяне на половин суматор се извършва два пъти. По подобен начин, когато решите да направите четирицифрен суматор, операцията се извършва още веднъж. С тази теория беше ясно, че внедряването е просто, но разработването отнема време.

Най-простият израз използва изключителната функция OR:

Сума = A XOR B

Носете = A И B

HA логическа диаграма

И еквивалентен израз по отношение на основните И, ИЛИ и НЕ е:

SUM = A.B + A.B ’

VHDL код за полуаддер

Обект ха е

Порт (a: в STD_LOGIC

b: в STD_LOGIC

sha: out STD_LOGIC

cha: out STD_LOGIC)

край ха

Архитектура Поведението на горната схема е

започнете

ша<= a xor b

не<= a and b

край Поведенчески

IC номер на половината суматор

Внедряването на половин суматор може да стане чрез високоскоростни CMOS цифрови логически интегрални схеми като серия 74HCxx, която включва SN74HC08 (7408) и SN74HC86 (7486).

Ограничения на половин суматор

Основната причина да извикате тези двоични суматори като Half Adders е, че няма обхват, който да включва бита за носене, използвайки по-ранен бит. Така че, това е основно ограничение на HA, използвани веднъж като двоичен сумиращ, особено в ситуации в реално време, които включват добавяне на няколко бита. Така че това ограничение може да бъде преодоляно, като се използват пълните суматори.

Пълно добавяне

Този сумата е труден за изпълнение в сравнение с полусума.

Функционална диаграма на пълния аддер

Разликата между полусъбирач и пълен суматор е, че пълният суматор има три входа и два изхода, докато половината суматор има само два входа и два изхода. Първите два входа са A и B, а третият вход е вход, носен като C-IN. Когато е проектирана логика на пълен суматор, вие нанизвате осем от тях заедно, за да създадете байтален суматор и каскадно пренасяте бита от един суматор към следващия.

FA таблица за истината

Износът на изхода е означен като C-OUT и нормалният изход е представен като S, което е „SUM“.

С горното пълна таблица на истината на разширител , изпълнението на пълна сумарна схема може да се разбере лесно. SUM ‘S’ се произвежда в две стъпки:

- Чрез XORing на предоставените входове „A“ и „B“

- Резултатът от A XOR B след това се XORed с C-IN

Това генерира SUM и C-OUT е вярно само когато или два от трите входа са HIGH, тогава C-OUT ще бъде HIGH. И така, можем да реализираме пълна схема на суматор с помощта на две половини вериги на суматор. Първоначално половината суматор ще се използва за добавяне на A и B, за да се получи частична сума, а логиката на втората половина суматор може да се използва за добавяне на C-IN към сумата, произведена от първата половина суматор, за да се получи окончателният S изход.

Ако някоя от логиката на полусъбирача произведе пренасяне, ще има изходно пренасяне. Така че, C-OUT ще бъде функция ИЛИ на изходите на полусумата Carry. Обърнете внимание на изпълнението на пълната схема на сумата, показана по-долу.

Пълна логическа диаграма на Adder

Въвеждането на по-големи логически диаграми е възможно с горната логика на пълния суматор, като най-често се използва по-прост символ за представяне на операцията. По-долу е дадено по-просто схематично представяне на еднобитов пълен суматор.

С този тип символ можем да добавим два бита заедно, като вземем пренасяне от следващия по-нисък порядък и изпращаме пренасяне към следващия по-висок порядък. В компютър, за многобитова операция, всеки бит трябва да бъде представен от пълен суматор и трябва да бъде добавен едновременно. По този начин, за да добавите две 8-битови числа, ще ви трябват 8 пълни суматори, които могат да бъдат оформени чрез каскадиране на два от 4-битовите блокове.

Половината и пълна добавка с помощта на K-Map

Дори резултатите от сумата и носенето за половин суматор също могат да бъдат получени с метода на картата на Karnaugh (K-map). The половин суматор и пълен суматор булев израз може да се получи чрез K-map. И така, K-картата за тези суматори е обсъдена по-долу.

Половината суматор K-карта е

HA K-Map

Пълният суматор K-Map е

FA K-Map

Логично изразяване на SUM и носене

Логическият израз на сумата (S) може да бъде определен въз основа на входните данни, споменати в таблицата.

= A’B’Cin + A ’B CCin’ + A B’Cin ’+ AB Cin

= Cin (A’B ’+ AB) + Cin’ (A’B + A B ’)

= Cin EX-OR (A EX-OR B)

= (1,2,4,7)

Логическият израз на пренасянето (Cout) може да бъде определен въз основа на входовете, споменати в таблицата.

= A’B Cin + AB’Cin + AB Cin ’+ ABCin

= AB + BCin + ACin

= (3, 5, 6, 7)

С гореспоменатите таблици на истината могат да се получат резултатите и процедурата е:

Комбинационна схема комбинира различните порти във веригата, където те могат да бъдат енкодер, декодер, мултиплексор и демултиплексор . Характеристиките на комбинационните вериги са както следва.

- Изходът във всеки момент от времето се базира само на нивата, които присъстват на входните терминали.

- Той не използва никаква памет. Предишното състояние на входа не оказва влияние върху настоящото състояние на веригата.

- Може да има произволен брой входове и m брой изходи.

VHDL кодиране

VHDL кодиране за пълен суматор включват следното.

обектът full_add е

Порт (a: в STD_LOGIC

b: в STD_LOGIC

cin: в STD_LOGIC

сума: излиза STD_LOGIC

cout: out STD_LOGIC)

край full_add

Архитектура Поведение на full_add е

компонент ха е

Порт (a: в STD_LOGIC

b: в STD_LOGIC

sha: out STD_LOGIC

cha: out STD_LOGIC)

краен компонент

сигнал s_s, c1, c2: STD_LOGIC

започнете

HA1: карта на порта на ха (a, b, s_s, c1)

HA2: карта на порта на ха (s_s, cin, sum, c2)

цена<=c1 or c2

край Поведенчески

The разлика между половината суматор и пълния суматор е, че половината суматор дава резултати, а пълният суматор използва половината суматор, за да получи някакъв друг резултат. По същия начин, докато Full-Adder е от два полусума, Full-Adder е действителният блок, който използваме за създаване на аритметични вериги.

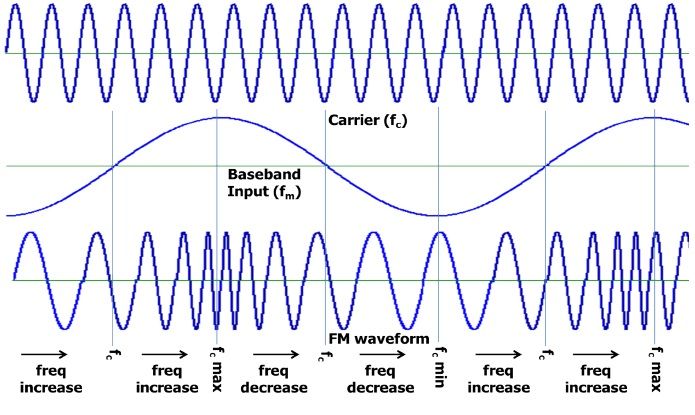

Носете добавки Lookahead

В концепцията за вериги за сушене на пулсации битовете, които са необходими за добавяне, са незабавно на разположение. Докато всяка секция на суматора трябва да държи времето си за пристигане на пренасяне от предишния блок на суматора. Поради това отнема повече време за създаване на SUM и CARRY, тъй като всяка секция във веригата чака пристигането на входа.

Например, за да достави изход за n-ия блок, той трябва да получи вход от (n-1)-ия блок. И това забавяне съответно се нарича закъснение на разпространението.

За да се преодолее закъснението в разширителния носител, беше въведен суматор за пренасяне-търсене. Тук, чрез използване на сложен хардуер, забавянето на разпространението може да бъде сведено до минимум. Диаграмата по-долу показва суматор за носене-преглед, използващ пълни суматори.

Носете Lookahead с помощта на пълен суматор

Таблицата на истината и съответните уравнения на изхода са

| ДА СЕ | Б. | ° С | C + 1 | Състояние |

| 0 | 0 | 0 | 0 | Не носи Генериране |

| 0 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | Не носи Разпространявайте |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | Носете Генериране |

| 1 | 1 | 1 | 1 |

Уравнението за разпространение се разпространява е Pi = Ai XOR Bi, а генерирането на пренасяне е Gi = Ai * Bi. С тези уравнения уравненията за сумиране и пренасяне могат да бъдат представени като

SUM = Pi XOR Ci

Ci + 1 = Gi + Pi * Ci

Gi доставя пренасяне само когато и двата входа Ai и Bi са 1, без да се има предвид входящото пренасяне. Pi е свързано с разпространението на пренасяне от Ci до Ci + 1.

Разлика между половината и пълния суматор

The разлика между таблицата с половин суматор и пълна суматор е показано по-долу.

| Половината добавяне | Пълно добавяне |

| Half Adder (HA) е комбинационна логическа схема и тази схема се използва за добавяне на две еднобитови цифри. | Full Adder (FA) е комбинационна схема и тази верига се използва за добавяне на три едноцифрени цифри. |

| В HA, след като преносът е генериран от предишното добавяне, не може да се добави към следващата стъпка. | В FA, след като пренасянето е генерирано от по-ранното добавяне, то може да бъде добавено към следващата стъпка. |

| Половината суматор включва два логически порта като AND порта и EX-OR порта. | Пълният разширител включва два EX-OR порта, два ИЛИ порта и два И порта. |

| Входните битове в полусъбирача са два като A, B. | Входните битове в пълния суматор са три като A, B & C-in |

| Половината суматор и уравнение за носене е S = a⊕b C = a * b | Пълният логически израз на суматора е S = a ⊕ b⊕Cin Cout = (a * b) + (Cin * (a⊕b)). |

| HA се използва в компютри, калкулатори, устройства, използвани за цифрови измервания и др. | FA се използва в цифрови процесори, многобитово добавяне и др. |

The ключови разлики между половината суматор и пълния суматор са обсъдени по-долу.

- Половината суматор генерира сума и пренос чрез добавяне на два двоични входа, докато пълният суматор се използва за генериране на сума и пренос чрез добавяне на три двоични входа. Както наполовина, така и хардуерната архитектура на пълния суматор не са еднакви.

- Основната характеристика, която отличава HA и FA, е, че в HA няма такава сделка, която да разглежда последното добавяне като неговия вход. Но FA намира конкретна входна колона като Cin, за да разгледа бита за носене на последното добавяне.

- Двата суматора ще покажат разлика въз основа на компонентите, използвани във веригата за нейната конструкция. Полусумарите (HA's) са проектирани с комбинацията от два логически порта като AND & EX-OR, докато FA е проектиран с комбинацията от три AND, две XOR & една OR порта.

- По принцип HA работят на 2-два входа от 1 бит, докато FA работят на три входа от 1 бит. Половината суматор се използва в различни електронни устройства за оценка на добавянето, докато пълният суматор се използва в цифровите процесори за добавяне на дълъг бит.

- Приликите в тези два суматора са, че и HA, и FA са комбинирани цифрови схеми, така че те не използват никакъв елемент от паметта като последователни вериги. Тези схеми са от съществено значение за аритметичната операция, за да осигурят добавяне на двоичното число.

Пълно внедряване на Adder с помощта на половин добавители

Внедряването на FA може да се осъществи чрез две полусумари, които са свързани логически. Блоковата схема на това може да бъде показана по-долу, което показва връзката на ФА с помощта на два полусума.

Уравненията за сумиране и пренасяне от предишни изчисления са

S = A ‘B’ Cin + A ’BC’ в + ABCin

Cout = AB + ACin + BCin

Уравнението на сумата може да бъде записано като.

Cin (A’B ‘+ AB) + C‘ in (A‘B + A B ’)

И така, Сума = Cin EX-OR (A EX-OR B)

Cin (A EX-OR B) + C’in (A EX-OR B)

= Cin EX-OR (A EX-OR B)

Cout може да се напише по следния начин.

COUT = AB + ACin + BCin.

Cout = AB + + разочарования BCIN (А + А)

= ABCin + AB + ACin + A ’B Cin

= AB (1 + Cin) + ACin + A ’B Cin

= A B + ACin + A ’B Cin

= AB + ACin (B + B ’) + A’ B Cin

= ABCin + AB + A’B Cin + A ’B Cin

= AB (Cin + 1) + A B Cin + A ’B Cin

= AB + AB ’Cin + A’ B Cin

= AB + Cin (AB ’+ A’B)

Следователно, COUT = AB + Cin (A EX-OR B)

В зависимост от горните две уравнения за суми и пренасяне, веригата FA може да бъде изпълнена с помощта на две HA и OR порта. Схемата на пълния суматор с две половин суматори е илюстрирана по-горе.

Пълно добавяне с помощта на две половини суматори

Пълен дизайн на Adder с използване на NAND Gates

Портата NAND е един вид универсална порта, използвана за изпълнение на всякакъв вид логически дизайн. FA веригата с диаграмата NAND Gates е показана по-долу.

FA използва NAND Gates

FA е лесен еднобитов суматор и ако искаме да изпълним добавянето на n-битов, тогава n не. на еднобитовите FA трябва да се използват във формата на каскадна връзка.

Предимства

The предимства на половин суматор и пълен суматор включват следното.

- Най-важната цел на половин суматор е да добави две еднобитови числа

- Пълните суматори притежават възможността да добавят бит за носене, който е резултат от предишното добавяне

- С пълен суматор могат да бъдат внедрени ключови схеми като суматор, мултиплексор и много други

- Веригите с пълен суматор консумират минимална мощност

- Предимствата на пълен суматор над половин суматор са, че пълният суматор се използва за преодоляване на недостатъка на половин суматор, тъй като половината суматор се използва главно за добавяне на две 1-битови числа. Половината суматори не добавят бита за носене, така че за да се преодолее този пълен суматор се използва. В пълен суматор, добавянето на три бита може да се направи и генерира два изхода.

- Проектирането на суматори е лесно и е основен градивен елемент, така че еднобитовото добавяне може лесно да бъде разбрано.

- Този суматор може да се преобразува в половин извадител чрез добавяне на инвертор.

- Чрез използване на пълен суматор може да се получи висока производителност.

- Висока скорост

- Много силно за мащабиране на захранващото напрежение

Недостатъци

The недостатъци на половин суматор и пълен суматор включват следното.

- В допълнение, половината суматор не може да използва преди носене, така че не е приложима за каскадно добавяне на мулти-бит.

- За да се преодолее този недостатък, FA е необходимо да се добавят три 1 бита.

- След като FA се използва под формата на верига като RA (Ripple Adder), тогава задвижващата способност на изхода може да бъде намалена.

Приложения

Приложенията на половин суматор и пълен суматор включват следното.

- Добавянето на двоични битове може да се извърши чрез наполовина суматор, използвайки ALU в компютъра, защото използва суматор.

- Комбинацията на половин суматор може да се използва за проектиране на пълна схема на суматор.

- Половината суматори се използват в калкулаторите и за измерване на адреси, както и таблици

- Тези схеми се използват за обработка на различни приложения в рамките на цифрови схеми. В бъдеще тя играе ключова роля в цифровата електроника.

- FA верига се използва като елемент в много големи вериги като Ripple Carry Adder. Този суматор добавя броя на битовете едновременно.

- FA се използват в единица за аритметична логика (ALU)

- FA се използват в свързани с графиката приложения като GPU (Graphics Processing Unit)

- Те се използват във веригата за умножение за изпълнение на умножение за пренасяне.

- В компютър, за генериране на адреса на паметта и за изграждане на програмния контрапункт към последващи инструкции, Аритметичната логическа единица се използва с помощта на Пълни добавящи.

По този начин, когато се добави две двоични числа, цифрите се добавят отначало най-малко бита. Този процес може да се извърши чрез половин суматор, защото най-простият n / w, който позволява добавяне на две 1-битови числа. Входовете на този суматор са двоични цифри, докато изходите са сумата (S) и носенето (C).

Винаги, когато се включи броят на цифрите, мрежата HA се използва просто за свързване на най-малкото цифри, тъй като HA не може да добави носещия номер от по-ранния клас. Пълният суматор може да бъде дефиниран като основа на всички цифрови аритметични устройства. Това се използва за добавяне на три едноцифрени числа. Този суматор включва три входа като A, B и Cin, докато изходите са Sum и Cout.

Свързани понятия

The понятия, свързани с половин суматор и пълен суматор просто не се придържайте към една цел. Те се използват широко в много приложения и са споменати някои от свързаните:

- Половин суматор и пълен суматор IC номер

- Разработване на 8-битов суматор

- Какви са предпазните мерки за половината суматор?

- JAVA Аплет на Ripple Carry Adder

Следователно това е всичко за теория на половин суматор и пълна суматор заедно с таблиците на истината и логическите диаграми е показан и дизайнът на пълен суматор, използващ половин верига суматор. Много от половин суматор и пълен суматор pdf налични са документи, които да предоставят разширена информация за тези концепции. Освен това е важно да знаете как се изпълнява 4-битов пълен суматор ?