Основният недостатък на комбинационна верига е, той не използва никаква памет за запазване на настоящото и предишните състояния. Следователно предишното състояние на входа не оказва влияние върху настоящото състояние на веригата. Докато последователната схема има памет, така че изходът може да варира в зависимост от входа. Този тип схеми използва предишен вход, изход, часовник и елемент от паметта. Тук елементите на паметта могат да бъдат резе или джапанки. Последователните вериги са проектирани по различни методи като използване на ROM и флипове, PLA, CPLD (сложно програмируемо логическо устройство) , FPGA (полеви програмируем портален масив) . В тази статия ще обсъдим само как да проектираме последователна верига, използвайки PLA.

Блоковата схема на последователната верига, както е показано по-долу:

Блок диаграма на последователна верига

Проектиране на последователна верига с използване на PLA

Последователни вериги може да се реализира с помощта на PLA (програмируеми логически масиви) и джапанки. При този дизайн държавното задание може да бъде важно, тъй като използването на добро състояние на държавата може да намали необходимия брой термини на продукта и следователно да намали необходимия размер на PLA. Продуктов термин, дефиниран като съвпад на литерали, където всеки литерал е или променлива, или нейното отрицание.

Нека разгледаме дизайна на преобразувател на код. Таблицата на състоянията, показана по-долу в таблицата, може да бъде реализирана чрез използване на един PLA и три джапанки както е показано по-долу на фигурата. Тази конфигурация на веригата е много подобна на дизайна, базиран на ROM тригер, с изключение на това, че ROM е заменен от PLA с подходящ размер. Заданието на държавата води до таблицата на истината, дадена по-долу. Тази таблица може да се съхранява в PLA с четири входа, 13 продуктови термина и четири изхода, но това би предложило малко намален размер в сравнение с ROM с 16 думи.

| X Q1 Q2 Q3 | С D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

Таблица: Таблица на истината

НАСТОЯЩО ДЪРЖАВА

| СЛЕДВАЩО СЪСТОЯНИЕ X = 0 1 | НАСТОЯЩО ИЗХОД (Z) |

| ДА СЕ | Б В | 1 0 |

Б. ° С | D E И Е | 1 0 0 1 |

д Е | Н Н Н М | 0 1 1 0 |

З. М | A A ДА СЕ - | 0 1 1 - |

Таблица: Държавна таблица

Проектиране на последователни вериги с помощта на PLA

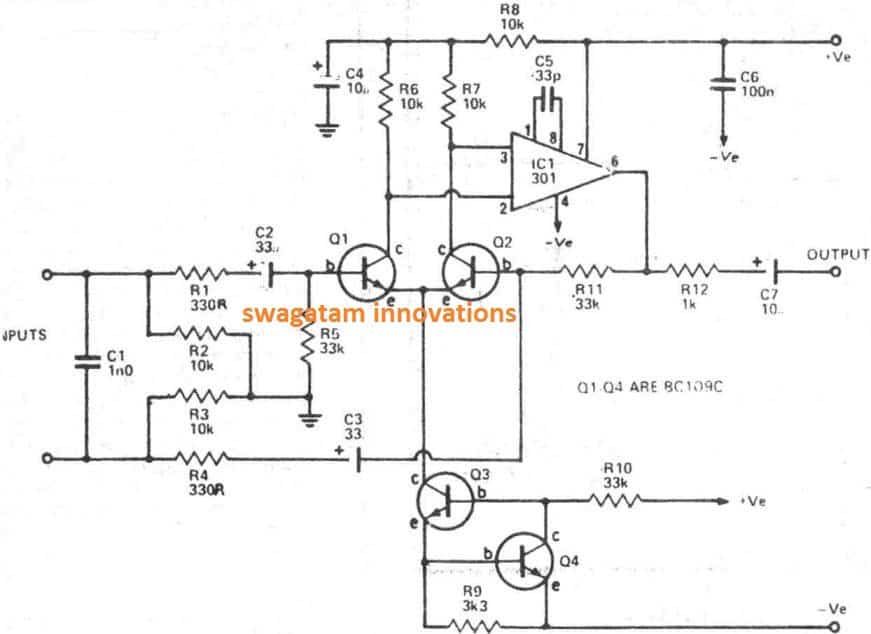

Входни изходни уравнения, изведени от Karnaugh Map

Тук, тъй като има седем състояния, са необходими три D джапанки. По този начин се изисква PLA схема с 4 входа и 4 изхода. Ако се разглежда присвояването на състоянието на преобразувателя на кода, полученото уравнение на изхода и D уравненията на тригера на тригера, получени от Karnaugh, могат да бъдат написани по следните уравнения

D1 = Q1 + = Q2 ”

D2 = Q2 + = Q2 ”

D3 = Q3 + = Q1 Q2 Q3 = X ”Q1 Q3” = X Q1 ”Q2”

Z = X ”Q3” + X Q3

| X Q1 Q2 Q3 | С D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 единадесет

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

Таблицата PLA, която съответства на тези уравнения, е дадена в таблицата по-горе. Тази таблица може да бъде реализирана чрез използване на PLA с четири входа, седем продуктови термина и четири изхода. За да проверите първоначално работата на горния дизайн, приемете, че X = 0 и Q1Q2Q3 = 000. Това избира редове - - 0- и 0 - - -0 в таблицата, така че Z = 0 и D1D2D3 = 100. След активния ръб на часовника, Q1Q2Q3 = 100. Ако следващият вход е X = 1, тогава се избират редове - - 0 - и - 1- -, така че Z = 0 и D1D2D3 = 110. След активния ръб на часовника, Q1Q2Q3 = 110.

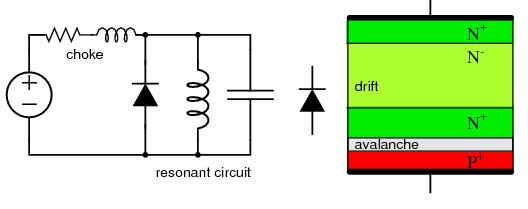

Програмируем логически масив (PLA)

Програмируем логически масив е програмируемо логическо устройство. Обикновено се използва за изпълнение на комбинационни логически схеми. PLA има набор от програмируеми И равнини (И масив), които се свързват с набор от програмируеми ИЛИ равнини (ИЛИ масив), които след това могат да бъдат временно допълнени, за да се получи изход. Това оформление позволява да се синтезират голям брой логически функции в сума от продукти (SOP) канонични форми. Проста блок-схема на PLA е дадена по-долу.

Блокова диаграма на PLA

Основната разлика между PLA и PAL (програмируема логика на масива) е,

PLA: И двете И равнина и ИЛИ равнина са програмируеми.

PAL: Само равнината И е програмируема, докато равнината ИЛИ е фиксирана.

За по-добро разбиране на PLA, тук разглеждаме примера по-долу.

Нека се опитаме да приложим тези функции f1 и f2 са дадени като

Входовете x1, x2, x3 и съответните им допълнени сигнали се дават на програмируема равнина И, там ще получим изходи И равнина като Р1, Р2, Р3, наречени минтерми. След това тези сигнали се подават в програмируема ИЛИ равнина, за да се получат необходимите изходни функции f1 и f2 (сума от продуктите). Фигурата по-долу описва внедряването на PLA на ниво порта за дадена функционалност.

Прилагане на PLA

Това е всичко за проектиране на последователни вериги с помощта на PLA. Считаме, че информацията, дадена в тази статия, е полезна за вас за по-доброто разбиране на тази концепция. Освен това, всякакви въпроси относно тази статия или каквато и да е помощ в изпълнение на електрически и електронни проекти , можете да се обърнете към нас, като коментирате в раздела за коментари по-долу. Ето въпрос към вас, Какво означава под последователна верига?