IC 4017 може да се разглежда като един от най-полезните и универсални чипове с множество приложения за електронни схеми.

За IC 4017

Технически се нарича десетилетен делител на десетилетие на Джонсън. Името предполага две неща, има нещо общо с номер 10 и броене / деление.

Числото 10 е свързано с броя на изходите, които този IC има, и тези изходи стават високо последователни в отговор на всеки висок тактов импулс, приложен на изхода на неговия входящ тактов сигнал.

Това означава, че всичките му 10 изхода ще преминат през един цикъл на високо изходно последователност от началото до края в отговор на 10 часовника, получени на неговия вход (пин # 14). Така че по някакъв начин това е броене и също разделяне на входния часовник на 10 и оттам името.

Разбиране на функцията на пиновете на IC 4017

Нека разберем подробно изводите на IC 4017 и от гледна точка на новодошлия: Поглеждайки фигурата, виждаме, че устройството е 16-пинов DIL IC, номерата на изводите са посочени в диаграмата със съответните им имена на задания.

Какво означават Logic High, Logic Low

Пиновете, които са маркирани като изходи, са щифтовете, които се представят логически „високо“ един след друг в последователност в отговор на тактови сигнали на пин # 14 на IC.

„Висока логика“ просто означава постигане на положителна стойност на захранващото напрежение, докато „логическа ниска“ се отнася до постигане на нулева стойност на напрежението.

Следователно с първия тактов импулс на пин # 14 първият изходен пиноут в реда, който е пин # 3, отива първо високо, след това се изключва и едновременно следващият пин # 2 става висок, след това този пин отива ниско и едновременно предходния щифт # 4 става висок ...... и така нататък, докато последният щифт # 11 стане висок.

Какъв е редът за секвениране на изходните щифтове?

За да бъдем точни, движението на последователността става чрез пиновете: 3, 2, 4, 7, 10, 1, 5, 6, 9, 11 ...

След пин # 11 IC вътрешно нулира и връща логиката високо на пин # 3, за да повтори цикъла.

Защо Pin 15 трябва да бъде заземен

Това секвениране и нулиране се извършва успешно само докато щифт # 15 е заземен или задържан на логически ниско ниво, в противен случай IC може да се повреди. Ако се държи високо, последователността няма да се случи и логиката на пин # 3 ще остане заключена.

Моля, обърнете внимание, че думата „високо“ означава положително напрежение, което може да бъде равно на захранващото напрежение на интегралната схема, така че когато казвам, че изходите стават високи по последователен начин, означава, че изходите произвеждат положително напрежение, което се измества последователно от един изходен щифт към следващия, по „работещ” DOT начин.

Pin 14 се нуждае от външна честота

Сега обясненото по-горе секвениране или изместване на изходната логика от един изходен щифт към следващия изход може да се изпълни само когато тактов сигнал се прилага към тактовия вход на интегралната схема, който е щифт # 14.

Не забравяйте, че ако към този входен щифт # 14 не е приложен часовник, той трябва да бъде присвоен или на положително захранване, или на отрицателно захранване, но никога не трябва да се държи окачен или несвързан, съгласно стандартните правила за всички CMOS входове.

Входният щифт на часовника # 14 реагира само на положителни часовници или положителен сигнал (нарастващ ръб) и с всеки следващ положителен пиков сигнал изходът на IC се измества или става висок в последователност, последователността на изходите е в реда на разпиновки # 3, 2, 4, 7, 10, 1, 5, 6, 9, 11.

Pin 13 е противоположен на Pin 14

ПИН # 13 може да се счита за противоположна на ПИН # 14 и този извод ще реагира на отрицателни пикови сигнали. Това означава, че ако към този щифт е приложен отрицателен часовник, това също ще доведе до изместване на „логически висок“ през изходните щифтове

Въпреки това обикновено този извод никога не се използва за прилагане на тактовите сигнали, вместо това извод № 14 се приема като стандартен вход за часовник.

Следователно на щифт # 13 трябва да бъде присвоен заземителен потенциал, което означава, че трябва да бъде свързан към земята, за да може IC да функционира.

В случай, че пин # 13 е свързан към положителен, целият IC ще спре и изходите ще спрат последователността и ще спрат да реагират на всеки тактов сигнал, приложен на пин # 14.

Как работи Pin 15 като нулиране на Pin

Pin № 15 на IC е входът за нулиране на щифта. Функцията на този щифт е да върне последователността обратно в първоначалното състояние в отговор на положителен потенциал или захранващо напрежение.

Това означава, че когато моментно положително напрежение удари щифт 15, изходната логическа последователност се връща към пин # 3 и започва цикъла отново.

Ако положителното захранване се държи свързано към този пин # 15, отново спира изхода от секвенирането и изходните скоби към пин # 3, което прави този пиноут висок и фиксиран.

Следователно, за да се направи функцията IC, щифт # 15 винаги трябва да бъде свързан към земята.

Ако този пиноут е предназначен да се използва като вход за нулиране , тогава той може да бъде закрепен към земята със сериен резистор от 100K или друга висока стойност, така че външното положително захранване вече може да бъде свободно въведено в него, когато се изисква нулиране на IC.

Пин # 8 е заземителният щифт и трябва да бъде свързан към минуса на захранването, докато щифт # 16 е положителен и трябва да бъде прекратен до положителното на захранващото напрежение.

ПИН # 12 е извършването и е без значение, освен ако много интегрални схеми са свързани последователно, ще го обсъдим някой друг ден. Пин # 12 може да бъде оставен отворен.

Имате конкретни въпроси ?? моля не се колебайте да ги попитате чрез вашите коментари ... всичко ще бъде разгледано щателно от мен.

Основна схема за свързване на изводите IC 4017

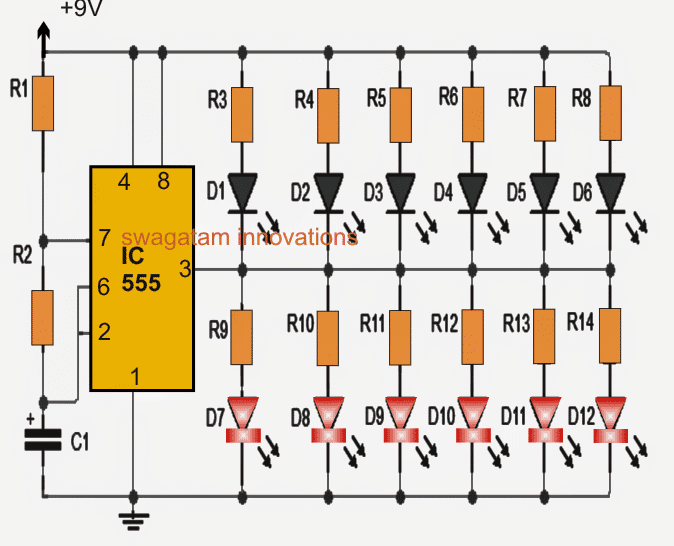

Приложение LED Chaser Circuit с помощта на IC 4017 и IC555

Следващият пример GIF схема показва как пиновете на IC 4017 обикновено са свързани с осцилатор за получаване на последователни логически високи изходи. Тук изходите са свързани към светодиоди за индикация на последователното изместване на логиката в отговор на всеки тактов импулс, генериран от генератора IC 555 на щифт # 14 на IC 4017.

Можете да видите, че логическото изместване се случва в отговор само на положителния часовник или положителния ръб на щифт # 14 на IC 4017. Последователността не реагира на отрицателните импулси или часовници.

IC 4017 Работна симулация

Видеоклип:

Предишен: Изграждане на прости транзисторни схеми Напред: Обяснени IC 4060 щифтове